CA Midterm_2 Review

Midterm_2 Review

Datapath & Controller

Pipeline

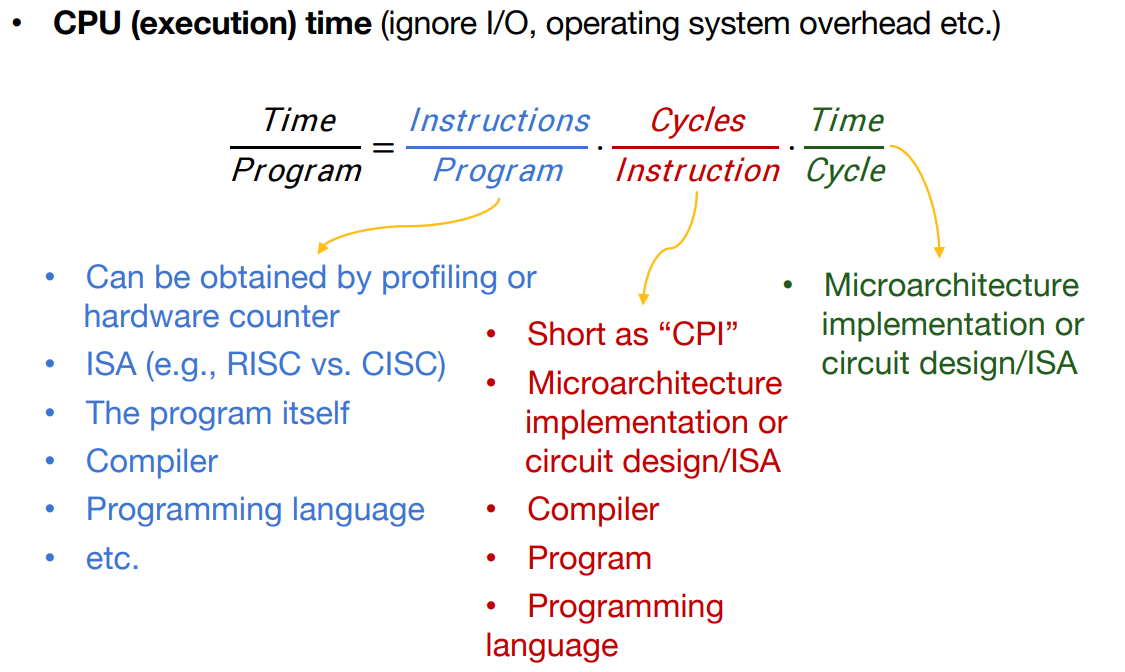

“Iron Law” Of Performance

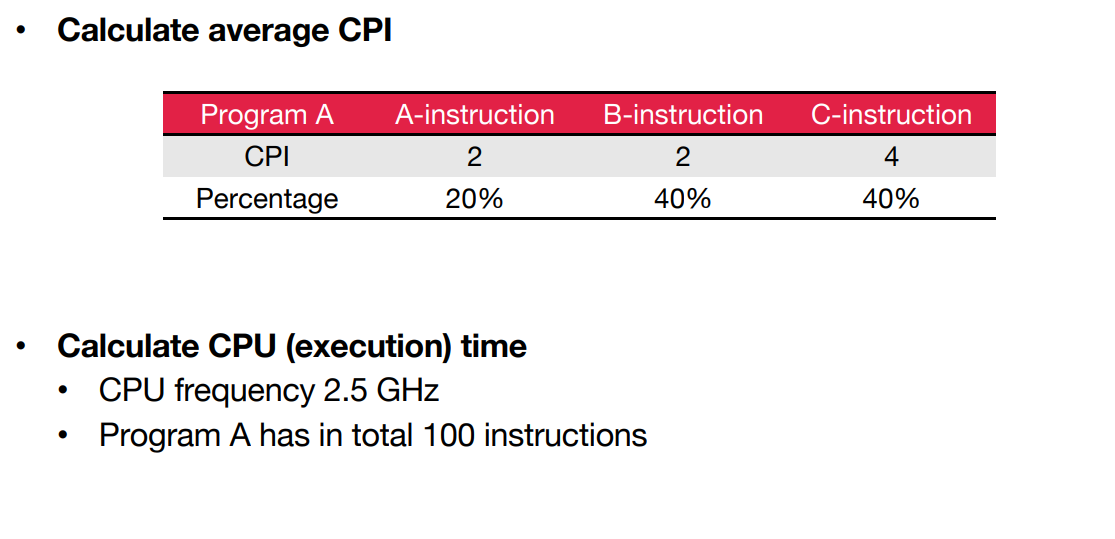

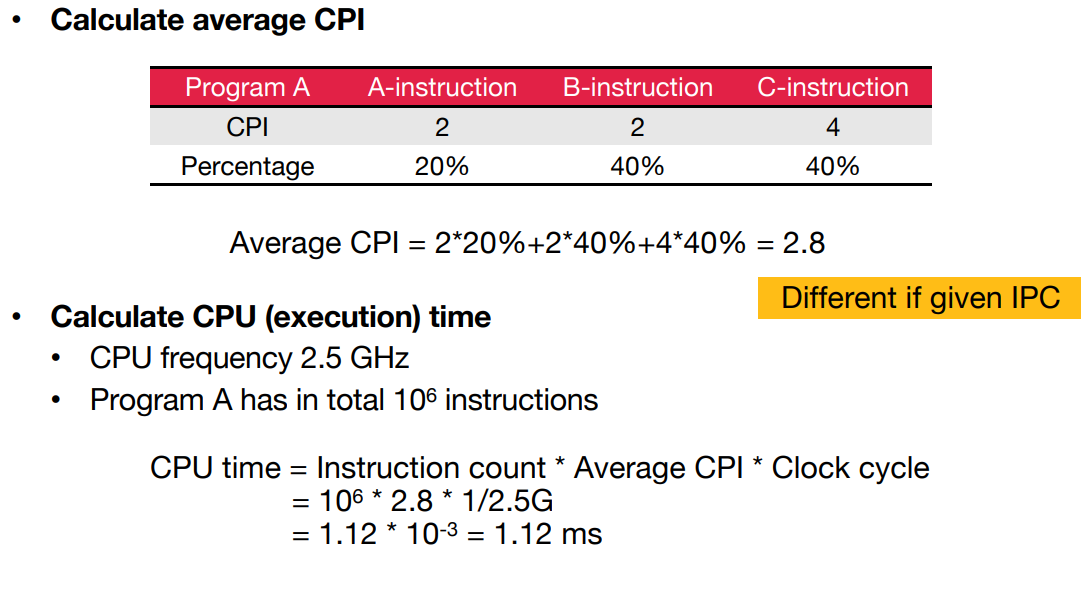

E.G

▶

Solution

注意各个部分的含义。

Hazards

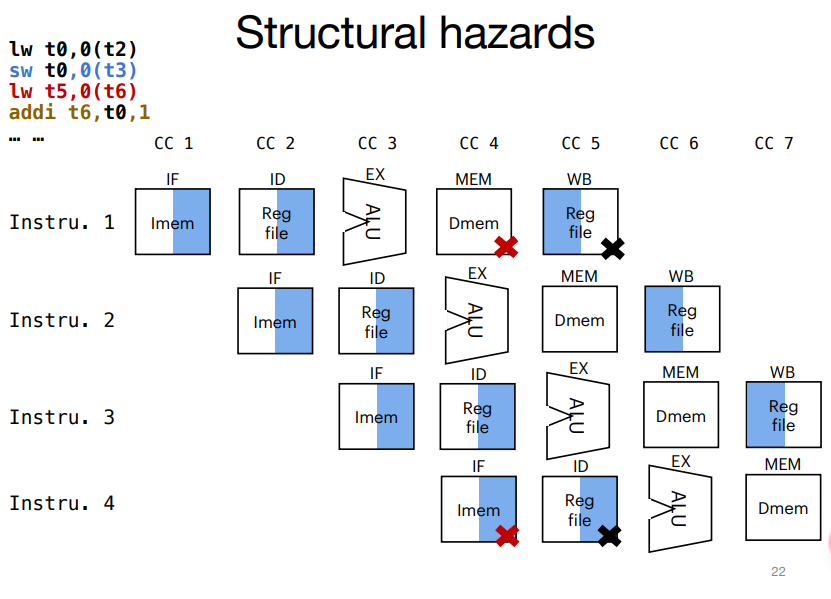

1. Structural Hazards

-

Abstract

由硬件限制引起的。Pipeline中的两个或更多指令争夺单个物理资源。 -

Solution:

- 指令和数据memory分开(Instruction cache and data cache)

- 增加硬件数量

- 设计硬件:寄存器在时钟上升沿写入,在后半个时钟周期任意读取 (in the textbook “the second half clock cycle”)

- Wait/Stall

2. Data Hazards

-

Abstract

- RAW(Read after write)

- WAW

- WAR

-

Solition:

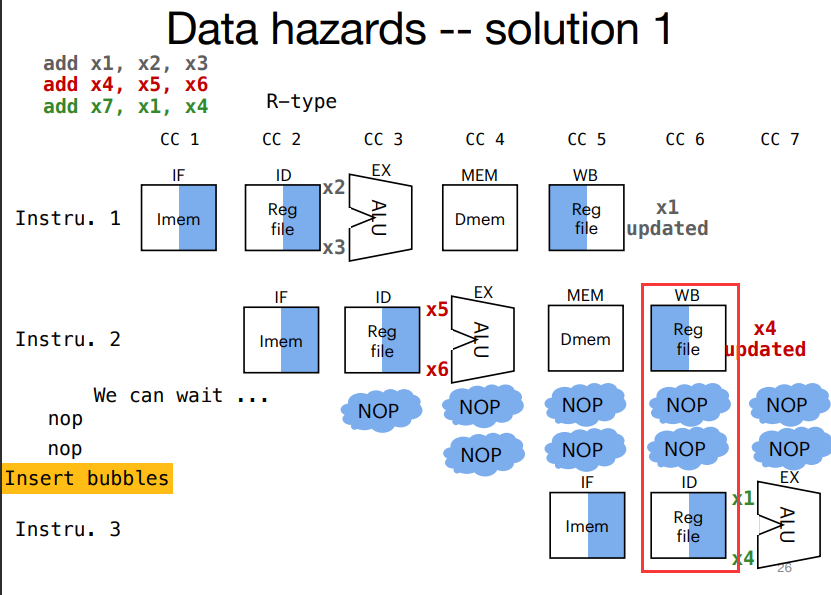

- Insert bubbles

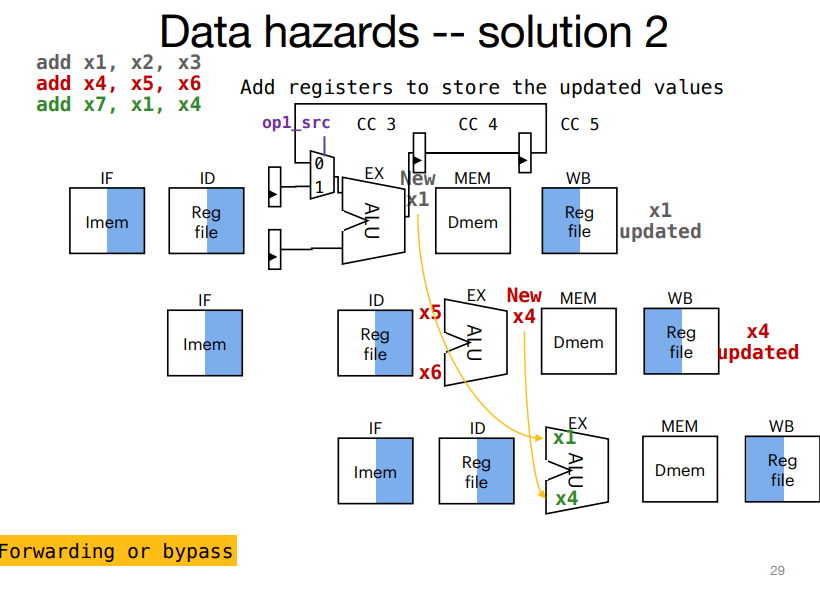

- Forwarding or bypass(寄存器)

How to decide op1_src?

第一个指令必须写入寄存器,第二指令、第三个指令必须读取寄存器。(分别对应ALU后和Dmem后的转发)

-

针对与

lw指令后的Data Hazards- Solution

- Wait/Stall

- Code scheduling

所以如果不重新排序,这里有一个不可避免的延迟。

- Solution

3. Control Harzards

CA Midterm_2 Review

http://lmehw.github.io/2024/04/22/CA-Midterm-2-Review/